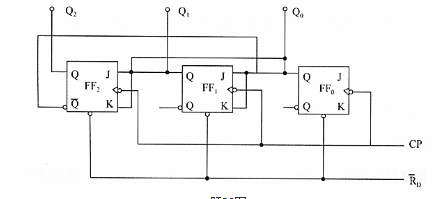

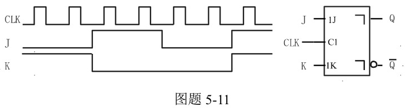

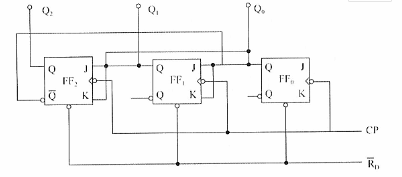

图所示逻辑电路,设触发器的初始状态均为0,当时,该电路实现的逻辑功能是( )。 A.同步十进制加法计数器 B.同步八进制加法计数器 C.同步六进制加法计数器 D.同步三进制加法计数器

题目

时,该电路实现的逻辑功能是( )。

B.同步八进制加法计数器

C.同步六进制加法计数器

D.同步三进制加法计数器

相似考题

更多“ 图所示逻辑电路,设触发器的初始状态均为0,当 ”相关问题

-

第1题:

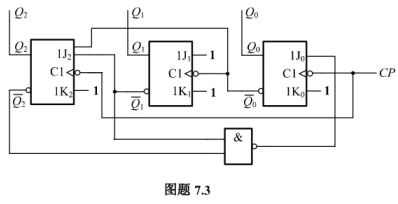

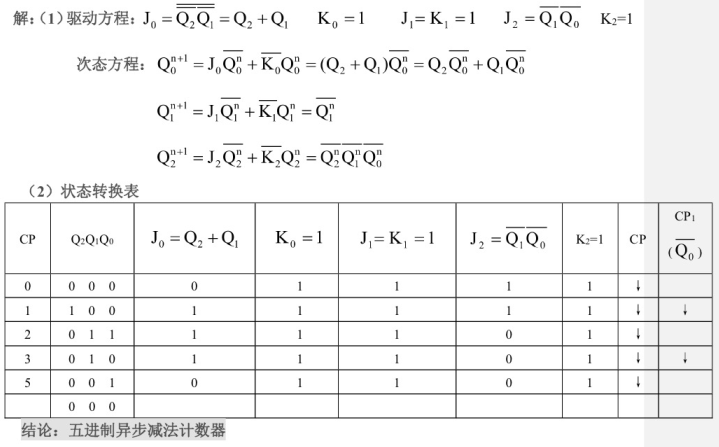

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:

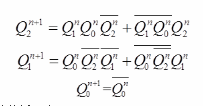

(1) 写出各触发器的驱动方程和次态方程;

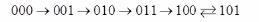

(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

参考答案:

参考答案:

-

第2题:

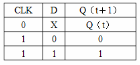

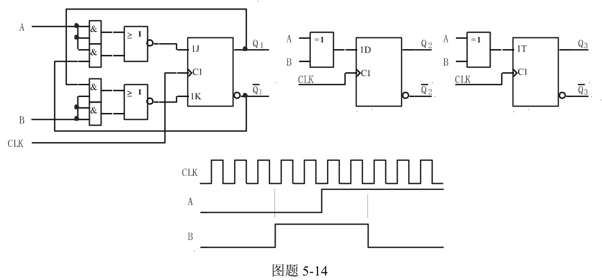

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第3题:

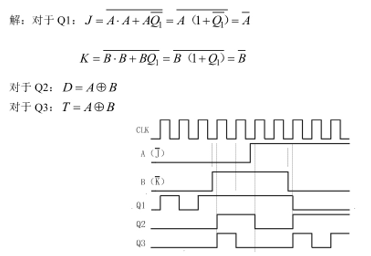

画出图题5-4所示的电平触发D触发器输出Q端的波形,输入端D与CLK的波形如图所示。(设0初始状太为0)

答案:

答案:

-

第4题:

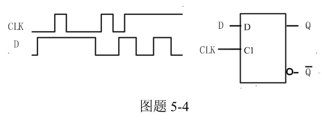

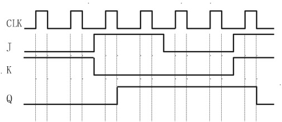

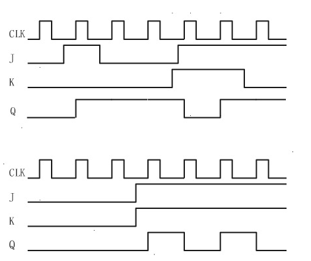

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第5题:

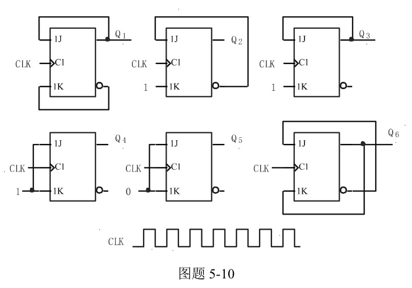

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第6题:

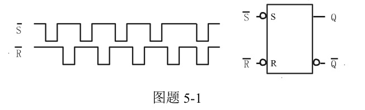

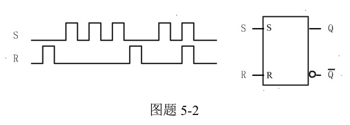

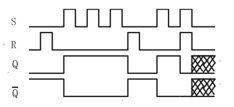

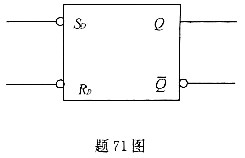

画出图题5-1所示的SR锁存器输出端Q、端的波形,输入端与的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第7题:

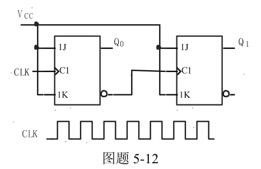

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第8题:

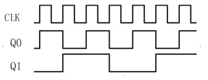

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第9题:

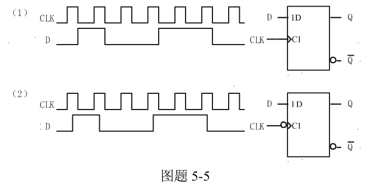

逻辑电路如图所示,当A=“0”,B=“1”时,C脉冲来到后,D触发器应( )。

A.具有计数功能

A.具有计数功能

B.保持原状态

C.置“0”

D.置“1”答案:A解析:“=1”为异或门的逻辑符号,即F=ab+ab -

第10题:

由两个主从型JK触发器组成的逻辑电路如图a)所示,设Q1、Q2的初始态是0、0, 已知输入信号A和脉冲信号CP的波形,如图b)所示,当第二个CP脉冲作用后,Q1、Q2将变为: A. 1、1

A. 1、1

B. 1、0

C. 0、1

D.保持0、0不变答案:C解析:提示:该触发器为负边沿触发方式,即:当时钟信号由高电平下降为低电平时刻输出端的状态可能发生改变。 -

第11题:

图所示逻辑电路,当A=0,B=1时,CP脉冲到来后D触发器( )。 A.保持原状态

A.保持原状态

B.置0

C.置1

D.具有计数功能答案:C解析:

-

第12题:

在如图7-72所示的RS触发器,设Q的初始状态为1,当输入X信号后,输出Q为()。

A.X B.X C.1 D.0答案:C解析:正确答案是C。

提示:任何触发器当没有CP脉冲时,都保持原状态。 -

第13题:

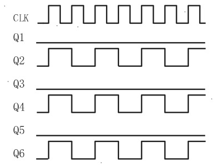

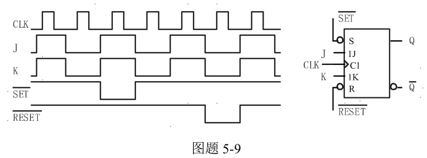

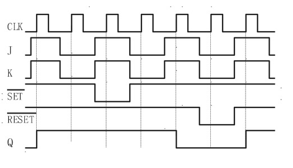

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第14题:

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

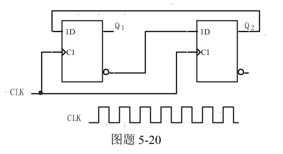

第15题:

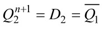

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第16题:

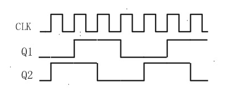

画出图题5-2所示的SR锁存器输出端Q、Q—端的波形,输入端S与R的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第17题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第18题:

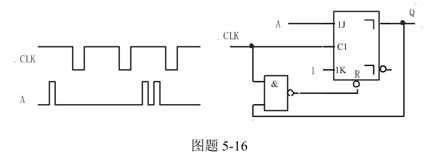

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第19题:

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

答案:

答案:

-

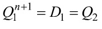

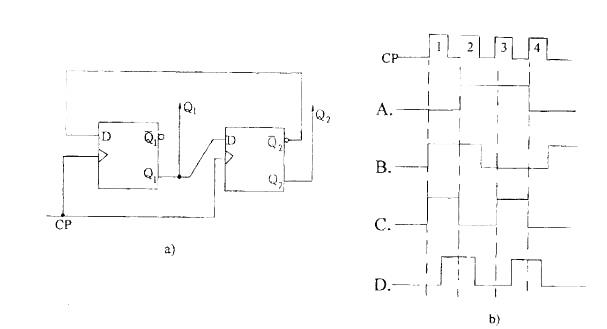

第20题:

D触发器组成的电路如图a)所示。设Q1、Q2的初始态是0、0,已知CP脉冲波型,Q2的波形是图b)中哪个图形? 答案:A解析:提示:从时钟输入端的符号可见,该触发器为正边沿触发方式。即:当时钟信号由低电平上升为髙电平时刻,输出端的状态可能发生改变,变化的逻辑结果由触发器的逻辑表决定。

答案:A解析:提示:从时钟输入端的符号可见,该触发器为正边沿触发方式。即:当时钟信号由低电平上升为髙电平时刻,输出端的状态可能发生改变,变化的逻辑结果由触发器的逻辑表决定。 -

第21题:

在图示逻辑电路中,触发器的初始状态是“1”态,当RD端保持高电平,在SD端加一负脉冲时,触发器的新态是( )。

A.翻转到“0”态

A.翻转到“0”态

B.保持“1”态

C.先翻转到“0”,马上回到“1”态

D.无规律翻转不能确定答案:B解析:基本RS触发器 -

第22题:

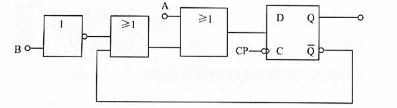

图所示逻辑电路,设触发器的初始状态均为“0”。当RD=1时,该电路的逻辑功能为( )。 A.同步八进制加法计数器

A.同步八进制加法计数器

B.同步八进制减法计数器

C.同步六进制加法计数器

D.同步六进制减法计数器答案:C解析:①组成:该电路由于CP端连在一起,因此是同步计数器;

②列写驱动方程:

③列写存储器状态方程:

④初始值为000,计数器CP释放脉冲后,计数循环为

故为同步六进制加法计数器。 -

第23题:

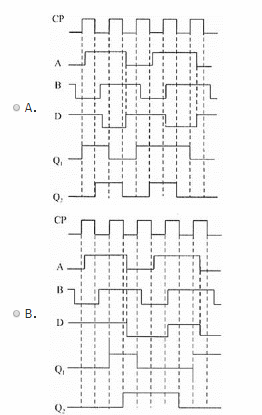

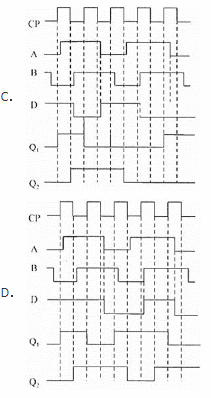

逻辑电路图及相应的输入CP、A、B的波形分别如图所示,初始状态Q1=Q2=0,当RD=1时,D、Q1、Q2端输出的波形分别是( )。

答案:A解析:首先分析D端输出,D的逻辑表达式为

答案:A解析:首先分析D端输出,D的逻辑表达式为

故只有当A=B=1时,D=0,可排除B、D项。D触发器为边沿触发器,特征表如题28解表所示,输出Q只在时钟信号边沿改变,分析可得,A、C选项的Q1端输出均为正确的。对于第二个JK触发器,它的时钟信号与CP相反,当Q1=1时,输出Q2在每个时钟信号的下降沿翻转;当Q1=0时,输出Q2在时钟信号的下降沿变为0,可得A项正确。