串行进位加法器运算速度比先行进位加法器慢。

题目

串行进位加法器运算速度比先行进位加法器慢。

相似考题

更多“串行进位加法器运算速度比先行进位加法器慢。”相关问题

-

第1题:

前进位加法器比串行进位加法器速度慢。()此题为判断题(对,错)。

参考答案:错误

-

第2题:

二进制并行加法器中,采用先行进位的目的是简化电路结构。()

参考答案:错误

-

第3题:

提高并行加法器速度的关键是尽量加快进位产生和传递的速度。()此题为判断题(对,错)。

正确答案:正确

-

第4题:

加法器有串行进位和()进位之分。参考答案:超前

-

第5题:

影响加法器运算速度的主要因素是(5)。

A.组成全加器的元器件的工作速度

B.串行进位链的总延迟时间

C.所有本地进位di产生的速度

D.所有全加和Qi产生的速度

正确答案:B

解析:本题考查加法器的组成。加法器的主要功能是对数进行加法运算,在大多数的中央处理器中,很多其他计算也是经过变换后使用加法器来完成的,一个位加法的逻辑图如下图所示。在上图中,Xi、Yi是加数和被加数;Ci+1是低位进位;Ci是进位;Zi是和。在加法运算器进行运算时,第f位的和除与本位操作数Xi和Yi有关外,还依赖.于低位进位信号,而低位进位信号依赖于更低位的进位信号,而这样的进位逻辑就是串行进位链。因此影响加法器运算速度的主要因素是串行进位链的总延迟时间,而加法器本身求和的延迟时间反而是次要的。 -

第6题:

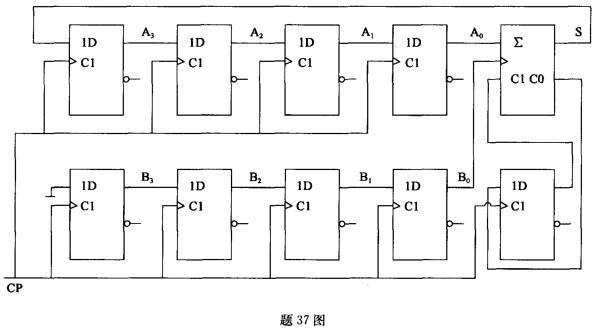

电路如图所示,该电路完成的功能是( )。

A. 8位并行加法器 B. 8位串行加法器

C. 4位并行加法器 D. 4位串行加法器答案:D解析:解加法器部分是A、B按位串行相加的。

答案:D -

第7题:

加法器采用并行进位的目的是()。

- A、提高加法器的速度

- B、快速传递进位信号

- C、优化加法器结构

- D、增强加法器功能

正确答案:B -

第8题:

半加法器和全加法器的区别是()。

- A、是否产生进位

- B、是否处理以前的进位

- C、是否产生和位

- D、是否处理以前的和位

正确答案:B -

第9题:

并行加法器采用超前进位的目的是简化电路结构。

正确答案:错误 -

第10题:

单选题74182芯片是一个()的进位链集成电路。A先行进位

B后行进位

C串行进位

D无进位

正确答案: D解析: 暂无解析 -

第11题:

单选题加法器采用并行进位的目的是()。A提高加法器的速度

B快速传递进位信号

C优化加法器结构

D增强加法器功能

正确答案: D解析: 暂无解析 -

第12题:

单选题与4位串行进位加法器比较,使用超前进位全加器的目的是()。A完成自动加法进位

B完成4位加法

C提高运算速度

D完成4位串行加法

正确答案: C解析: 暂无解析 -

第13题:

用八片74181和两片74182可组成________。

A.组内并行进位、组间串行进位的32位ALU

B.二级先行进位结构的32位ALU

C.组内先行进位、组间先行进位的16位ALU

D.三级先行进位结构的32位ALU

正确答案:B

-

第14题:

超前进位加法器比行波加器要简单()

参考答案错误

-

第15题:

74182芯片是一个()的进位链集成电路。A、先行进位

B、后行进位

C、串行进位

D、无进位

参考答案:A

-

第16题:

半加法器和全加法器的区别是

A. 是否产生进位

B. 是否处理以前的进位

C. 是否产生和位

D. 是否处理以前的和位

正确答案:B

-

第17题:

用8片741 81和2片74182DT。可组成( )。

A.采用组内并行进位、组间串行进位结构的32位ALU

B.采用二级先行进位结构的32位ALU

C.采用组内先行进位、组间先行进位结构的16位ALU

D.采用三级先行进位结构的32位ALU

正确答案:B

-

第18题:

在串行进位的并行加法器中,影响加法器运算速度的关键因素是()。A.门电路的级延迟

B.元器件速度

C.进位传递延迟

D.各位加法器速度的不同答案:C解析:加法器是整个运算器的核心,提高加法器的运算速度最直接的方法就是多位并行加法。本题中4个选项均会对加法器的速度产生影响,但只有进位传递延迟对并行加法器的影响最为关键。 -

第19题:

乘法器的硬件结构通常采用()

- A、串行加法器和串行移位器

- B、并行加法器和串行左移

- C、并行加法器和串行右移

- D、串行加法器和串行右移

正确答案:C -

第20题:

采用串行加法器比采用并行加法器的运算速度快。

正确答案:错误 -

第21题:

与4位串行进位加法器比较,使用超前进位全加器的目的是()。

- A、完成自动加法进位

- B、完成4位加法

- C、提高运算速度

- D、完成4位串行加法

正确答案:C -

第22题:

单选题A8位并行加法器

B8位串行加法器

C4位并行加法器

D4位串行加法器

正确答案: D解析: -

第23题:

单选题加法器中进位产生函数是()AAi+Bi

BAi⊕Bi

CAi-Bi

DAiBi

正确答案: D解析: 暂无解析 -

第24题:

单选题半加法器和全加法器的区别是()。A是否产生进位

B是否处理以前的进位

C是否产生和位

D是否处理以前的和位

正确答案: D解析: 暂无解析