设计一个8位二进制加法/减法计数器, clr为计数器同步复位端,clr=0时,计数器清零,load是同步预置控制端,高电平有效。en为使能控制输入端,高电平时,计数器可进行加或减计数,up_down为加减控制端,up_down=1加法计数,up_down=0减法计数,clk为时钟端,data[7:0]为预置的数据端,q[7:0]为计数器的输出端。

题目

设计一个8位二进制加法/减法计数器, clr为计数器同步复位端,clr=0时,计数器清零,load是同步预置控制端,高电平有效。en为使能控制输入端,高电平时,计数器可进行加或减计数,up_down为加减控制端,up_down=1加法计数,up_down=0减法计数,clk为时钟端,data[7:0]为预置的数据端,q[7:0]为计数器的输出端。

相似考题

更多“设计一个8位二进制加法/减法计数器, clr为计数器同步复位端,clr=0时,计数器清零,load是同步预置控制端,高电平有效。en为使能控制输入端,高电平时,计数器可进行加或减计数,up_down为加减控制端,up_down=1加法计数,up_down=0减法计数,clk为时钟端,data[7:0]为预置的数据端,q[7:0]为计数器的输出端。”相关问题

-

第1题:

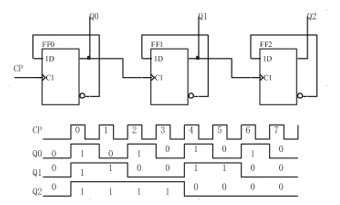

试用上升沿D触发器构成异步3位二进制加法计数器,要求画出逻辑电路图,以及计数器输入时钟CLK与D触发器输出端Q2~Q0的波形图。答案:

-

第2题:

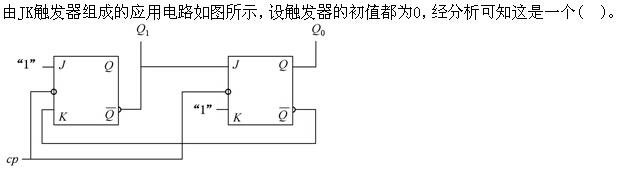

A.同步二进制加法计数器

A.同步二进制加法计数器

B.同步二进制减法计数器

C.异步二进制减法计数器

D.异步二进制加法计数器答案:C解析:CP没有接到所有触发器的时钟端,因此是异步时序电路,具有减法规律。 -

第3题:

复位法是利用计数器芯片的哪个端构成任意进制计数器的方法?( )A.复位端

B.预置数端

C.进(借)位输出端答案:A解析: -

第4题:

在监视回答编码脉冲间隔时,在同步间隔存在期间,使用可预置的减计数器监视时钟计数,当同步间隔脉冲结束时,10微秒和1微秒的减计数器的借位(CT)输出分别为()时,说明间隔在公差范围之内。

- A、0(低电平)和0(低电平)

- B、0(低电平)和1(高电平)

- C、1(高电平)和0(低电平)

- D、1(高电平)和1(高电平)

正确答案:A -

第5题:

如果按计数器翻转的次序来分类,可把计数器分为()。

- A、加法计数器

- B、减法计数器

- C、异步式计数器

- D、同步式计数器

正确答案:C,D -

第6题:

计数器按计数工作方式分为()。

- A、同步计数器和异步计数器

- B、二进制计数器和非二进制计数器

- C、加法计数器和减法计数器

- D、扭环形计数器和环形计数器

正确答案:C -

第7题:

如果计数器的计数脉冲不是同时加到所有触发器的计数输入端,而只加到最低位触发器的计数输入端,其他各级触发器则由相邻的低位触发器来触发,这时计数器称为()。

- A、同步计数器;

- B、异步计数器;

- C、可逆计数器;

- D、步计数器。

正确答案:B -

第8题:

模为2的正整数次幂的二进制递增计数器,若从其反向输出端Q输出,则得()同模计数器。

正确答案:二进制递减 -

第9题:

定时器8253的门控信号GATE作用是门控输入端,用于外部控制计数器的启动或停止计数的操作,()的作用是计数器的时钟脉冲输入端,用于输入定时脉冲或计数脉冲信号,OUT端作用是定时器的输出端。

正确答案:CLK端 -

第10题:

将两片CC40192级联后用借位输出法构成M(M<=100)进制减法计数器,预置数端的数据N应是M。

正确答案:正确 -

第11题:

计数器的两个输入端是()。

- A、计数输入端和输出端

- B、复位端和计数输入端

- C、复位端和移位端

- D、计数输出端和复位端

正确答案:B -

第12题:

填空题当减计数器的复位输入端有效时,计数器自动进行复位,计数器的位为OFF当前值复位为()。正确答案: 预设置解析: 暂无解析 -

第13题:

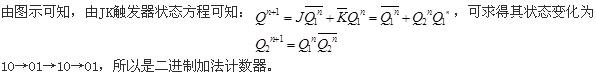

A.同步二进制加法计数器

A.同步二进制加法计数器

B.同步四进制加法计数器

C.同步三进制计数器

D.同步三进制减法计数器答案:A解析:

-

第14题:

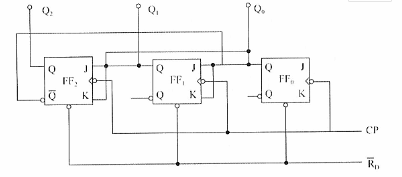

图所示逻辑电路,设触发器的初始状态均为“0”。当RD=1时,该电路的逻辑功能为( )。 A.同步八进制加法计数器

A.同步八进制加法计数器

B.同步八进制减法计数器

C.同步六进制加法计数器

D.同步六进制减法计数器答案:C解析:①组成:该电路由于CP端连在一起,因此是同步计数器;

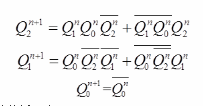

②列写驱动方程:

③列写存储器状态方程:

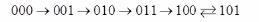

④初始值为000,计数器CP释放脉冲后,计数循环为

故为同步六进制加法计数器。 -

第15题:

用同步状态译码预置数法构成M进制加法计数器,若预置数据为0,则应将什么所对应的状态译码后驱动预置数控制端?( )A.M

B.M-l

C.M+l答案:B解析: -

第16题:

回答效率的监视是将测试询问PRF的60%脉冲和同步回答脉冲作为时钟分别加到加、减计数器的()端。

- A、CPD、CPU

- B、CPU、CPD

- C、CPD、预置

- D、CPU、预置

正确答案:B -

第17题:

环形计数器的特点是()。

- A、环形计数器的有效循环中,每个状态只含一个1或0

- B、环形计数器的有效循环中,每个状态只含一个1

- C、环形计数器的有效循环中,每个状态只含一个0

- D、环形计数器中,反馈到移位寄存器的串行输入端Dn-1的信号是取自Q0

- E、环形计数器中,反馈到移位寄存器的串行输入端Dn的信号是取自Q0

正确答案:B,D -

第18题:

8253芯片上有()个()位计数器通道,每个计数器有()种工作方式可供选择。若设定某通道为方式0后,其输出引脚OUT为()电平;当()后通道开始计数,()信号端每来一个脉冲()就减1;当(),则输出引脚输出()电平,表示计数结束。

正确答案:3;16;6;低;写入计数初值;脉冲输入CLK;减法计数器;计数器的计数值减为0;高 -

第19题:

在加计数器的设置输入S的(),将预置值PV指定的值送入计数器字。在加计数脉冲CU的上升沿,如果计数值小于999,计数值加1。复位输入端R为1时,计数值被清零。计数值大于0时,计数器位(Q)为1;计数值为0时,计数器位为()。

正确答案:上升沿;0 -

第20题:

按照计数器中各触发器状态更新的情况不同,可将计数器分为()。

- A、同步计数器

- B、加法计数器

- C、减法计数器

- D、异步计数器

正确答案:A,D -

第21题:

既可以作为加法计数器又可以作为减法计数器的是()

- A、同步计数器

- B、异步计数器

- C、可逆计数器

- D、集成计数器

正确答案:C -

第22题:

n位环形计数器的特点是()

- A、环形计数器的有效循环中,每个状态只含一个1或0

- B、环形计数器的有效循环中,每个状态只含一个1

- C、环形计数器的有效循环中,每个状态只含一个0

- D、环形计数器中,反馈到移位寄存器的串行输入端Dn-1的信号是取自Q0

- E、环形计数器工作时,应避免每个状态可以都是1或都是0

正确答案:A,D,E -

第23题:

同步计数器和异步计数器的区别是()。

- A、前者各触发器的触发脉冲相同,而后者不同

- B、前者有同步清零端,而后者有异步清零端

- C、前者有同步置数端,而后者异步置数端

- D、前者靠同步输入端控制计数规律,而后者靠异步输入端控制计数规律

正确答案:A -

第24题:

单选题既可以作为加法计数器又可以作为减法计数器的是()A同步计数器

B异步计数器

C可逆计数器

D集成计数器

正确答案: C解析: 暂无解析