8、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。

题目

8、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。

相似考题

参考答案和解析

更多“8、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。”相关问题

-

第1题:

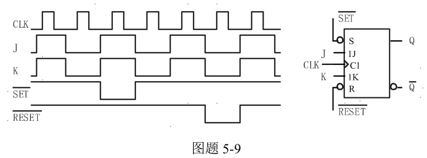

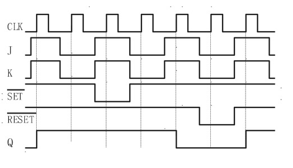

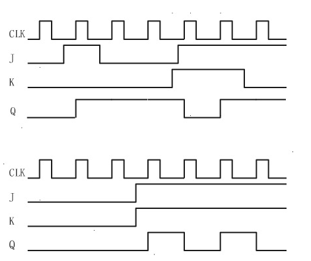

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第2题:

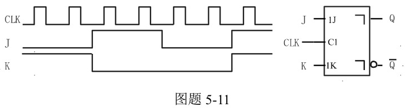

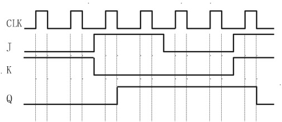

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第3题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第4题:

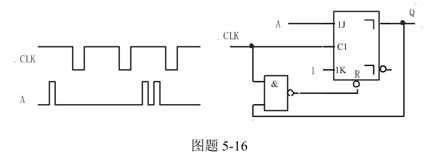

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第5题:

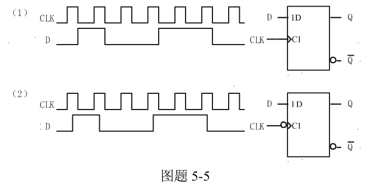

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第6题:

一般规定用触发器的()端作为触发器的状态,Q=1时,称触发器处于()态。Q=0时称触发器处于()态。

正确答案:Q;1;0 -

第7题:

无论J-K触发器原来状态如何,当输入端J=1、K=0时,在时钟脉冲作用下,其输出端Q的状态为()。

- A、0

- B、1

- C、保持不变

- D、不能确定

正确答案:B -

第8题:

基本的R-S触发器两个输入端R=1、S=1,输出端Q=()。

- A、维持原状态

- B、1

- C、0

正确答案:A -

第9题:

当基本RS触发器的R=1,S=0时,Q端处于()。

- A、0状态

- B、1状态

- C、原状态

- D、不确定

正确答案:B -

第10题:

当基本RS触发器的R=S=0时,Q端处于()。

- A、0状态

- B、1状态

- C、原状态

- D、不确定

正确答案:D -

第11题:

一个同步RS触发器,R为复位端,S为置位端,它们均为低电平有效,若CP=0,R=1,S=0,则该触发器Q端的状态()

- A、维持不变

- B、变为0

- C、变为1

- D、无法判断

正确答案:A -

第12题:

同步计数器和异步计数器的区别是()。

- A、前者各触发器的触发脉冲相同,而后者不同

- B、前者有同步清零端,而后者有异步清零端

- C、前者有同步置数端,而后者异步置数端

- D、前者靠同步输入端控制计数规律,而后者靠异步输入端控制计数规律

正确答案:A -

第13题:

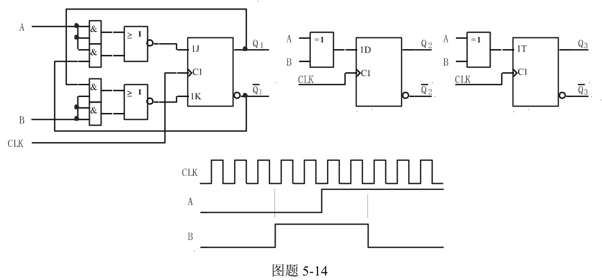

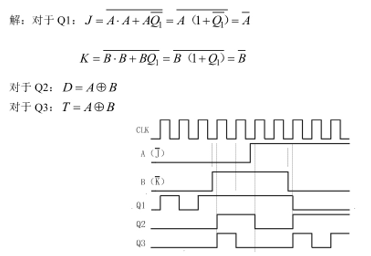

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第14题:

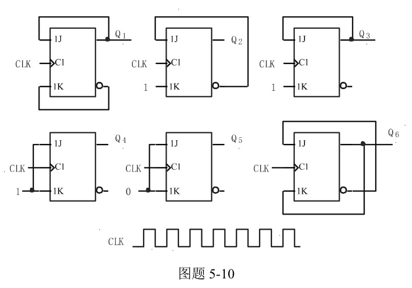

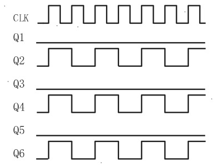

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第15题:

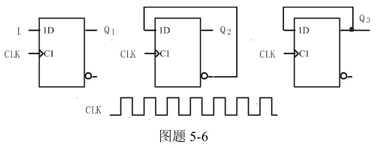

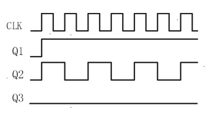

画出图题5-6所示的边沿D触发器输出Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

答案:

答案:

-

第16题:

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

答案:

答案:

-

第17题:

一个基本的R5触发器,R为复位端,S为置位端,它们均为低电平有效。若R=1,S=0,则该触发器Q端的状态是()。

- A、D

- B、不定

- C、1

- D、在0与1之间振荡

正确答案:C -

第18题:

PLC的RS触发器功能和电子RS触发器完全一样,都是S端有效触发器置1,R端有效复位。

正确答案:错误 -

第19题:

钟控R-S触发器当(),时,触发器输出Q端为

- A、置0功能

- B、置1功能

- C、保持功能

- D、禁止状态

正确答案:C -

第20题:

触发器的两个输出端输出状态必须()

- A、相同

- B、相反

- C、记忆

- D、输出

正确答案:B -

第21题:

下列说法正确的是()。

- A、一个触发器可以有一个输出端,也可以有两个输出端

- B、触发器两个输出端的电平可以相同,也可以相反

- C、时钟信号决定了触发器的翻转时刻,控制输入信号决定了触发器翻转后的状态

- D、时钟脉冲信号的触发都是上升沿触发

正确答案:C -

第22题:

一个只有单端输入的边沿触发器,输入信号为0,原来所处状态Q=1,在时钟信号改变时,触发器状态Q变为0,则该触发器为()。

- A、RS触发器

- B、JK触发器

- C、D触发器

- D、T触发器

正确答案:C -

第23题:

规定RS触发器()的状态作为触发器的状态。

- A、R端

- B、S端

- C、Q端

正确答案:C -

第24题:

单选题下列说法正确的是()。A一个触发器可以有一个输出端,也可以有两个输出端

B触发器两个输出端的电平可以相同,也可以相反

C时钟信号决定了触发器的翻转时刻,控制输入信号决定了触发器翻转后的状态

D时钟脉冲信号的触发都是上升沿触发

正确答案: C解析: 暂无解析